## BE (IT) Part II 3<sup>rd</sup> Semester Examination 2011

## IT305: Digital Circuits and Logic Design

Answer Question No. 1 and any FIVE from the rest

FM-70 Duration: 3 hr

## 1. Answer the following:

$10 \times 2$

- a. Perform the binary addition: 11000.11 + 101.111. Also carry out the equivalent decimal addition.

- b. Perform the subtraction with the following binary numbers by 2's complement method. Check the answer by straight subtraction.

100 - 110000

c. Convert the following to the other canonical form:

$$F(x, y, z) = \Sigma(0, 2, 4, 6)$$

d. The Boolean expressions of the two variables X and Y in terms of the three inputs A, B and C are given by

$$X = ABC + \overline{A}B\overline{C} + A\overline{B}\overline{C}$$

$$Y = (\overline{A} + \overline{B} + \overline{C})(\overline{A} + B + C)(A + \overline{B} + C)$$

What is the relationship between X and Y?

- e. An equality detector gives the output Y = 1 if both the inputs A and B are either 0 or 1. Construct the truth table and write the Boolean expression for Y.

- f. Show how to implement AND with OR and NOT gates?

- g. Show that the dual of the exclusive-OR is equal to its complement.

- h. Show that a positive-logic AND gate is a negative-logic OR gate, and vice versa.

- i. Give the truth table of 3-input XNOR gate.

- j. Simplify the Boolean function (using K-map):  $f(x, y, z) = \Sigma(0, 3, 5, 7)$

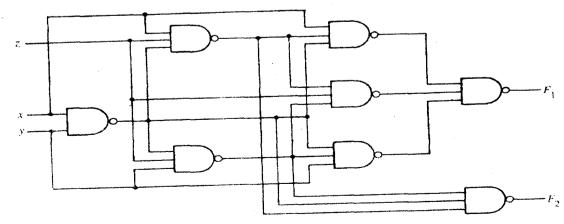

- 2. Determine the output Boolean functions of the circuit in the following figure:

Obtain the truth table for the above circuit.

Obtain the equivalent AND-OR logic diagram of the above figure.

3. Design a combinational circuit that compares two 4-bit numbers, A and B, to check if they are equal. The circuit has one output x, so that x = 1 if A = B, and x = 0 if  $A \neq B$ . Clearly depict the diagram and explain its operation.

5 + 5

4. a) A combinational circuit is defined by the following two functions:

$$F_1(x, y) = \Sigma(1, 3)$$

$F2(x, y) = \Sigma(0, 2, 3)$

Implement the combinational circuit by means of the decoder and external NAND gates.

b) Construct a  $5 \times 32$  decoder with four  $3 \times 8$  decoders and a  $2 \times 4$  decoder. Use a block diagram construction.

5 + 5

- 5. A burglar alarm should activate when the two conditions given below are simultaneously satisfied:

- a) The main entrance door of the building is open, and

- b) The bedroom door and / or the kitchen door is open.

Write the truth table and construct the logic circuit to operate the alarm using one AND gate and one OR gate.

4 + 6

6. What is triggering? Classify different types of triggering. What type of triggering is used in conventional DDR RAM? Implement the expression for the output carry and sum of a 1 bit full adder circuit using a PLA.

1+2+1+6

7. What is race around condition in context to JK flip flop? Explain. How this problem is overcome? Explain with block diagram.

4+6

8. What are the differences between synchronous and asynchronous sequential circuits? Explain the principle of operation of a clocked SR flip flop with preset and clear inputs. Mention major applications of flip flops.

3+4+3

9. Explain the principle of operation of a 4 bit PISO register. How many clock cycles will be required to transfer an 8 bit data block to this register? Mention some merits and demerits of Ring counter and Johnson's counter.